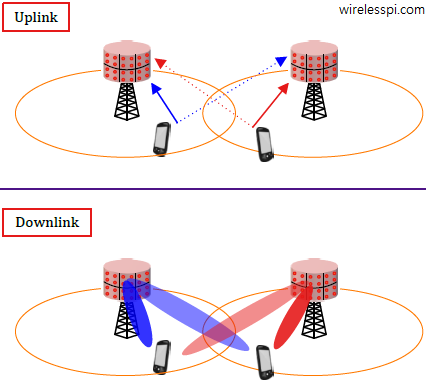

5G NR standard supports both Frequency Division Duplex (FDD) and Time Division Duplex (TDD) modes in massive MIMO systems. For a reasonably pure estimate, it is necessary to make sure that each pilot transmission in a cell occurs in a vacuum, i.e., free from the interference of other pilots in the same time or frequency. This is achieved through orthogonality or separation of training signals in time or frequency slots. As we see now, simple orthogonality is not enough and new problems emerge due to the interaction among different cells in a network. Uplink A set of orthogonal pilots in

Continue reading