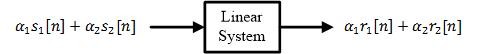

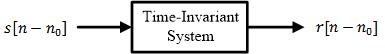

In wireless communications and other applications of digital signal processing, we often want to modify a generated or acquired signal. A device or algorithm that performs some prescribed operations on an input signal to generate an output signal is called a system. Amplifiers in communication receivers and filters in image processing applications are some systems that we interact with in daily lives. Our main focus in these articles will be on a particular class of systems which are linear and time-invariant. A linear system implies that if two inputs are scaled and summed together to form a new input, the

Continue reading