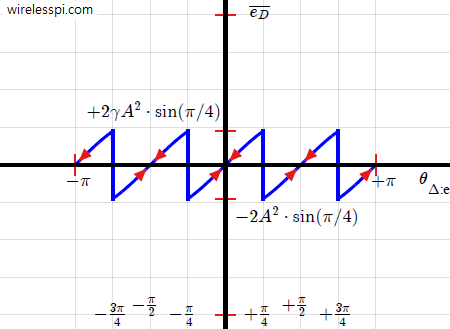

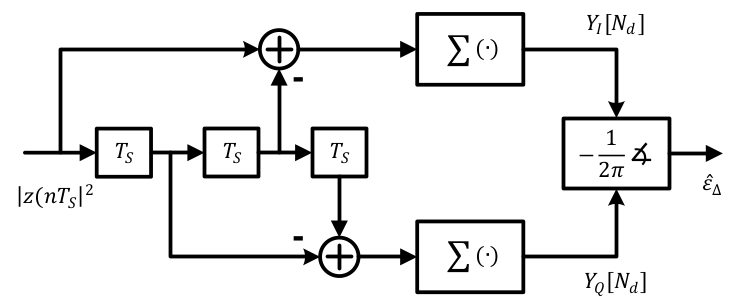

In a previous article, we have covered in detail the inner workings of a Phase Locked Loop (PLL) in a Software Defined Radio (SDR). There are two phenomena that have the potential to occasionally disrupt the performance of a PLL operating in steady state: cycle slips and hangup. Both the carrier and timing locked loops suffer from these issues. The underlying mathematics is quite intricate and hence I give a simple overview of these concepts. A reader interested in further exploration is referred to [1]. Cycle Slips To understand the cycle slip, assume that the loop is in tracking mode,

Continue reading