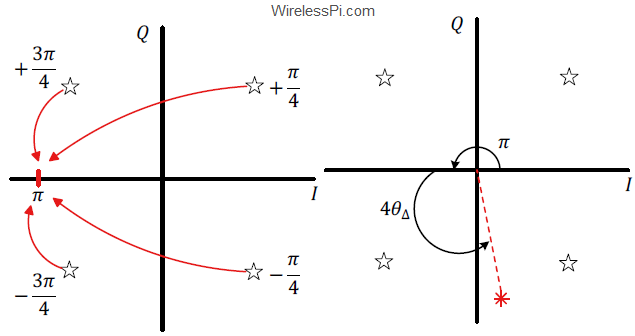

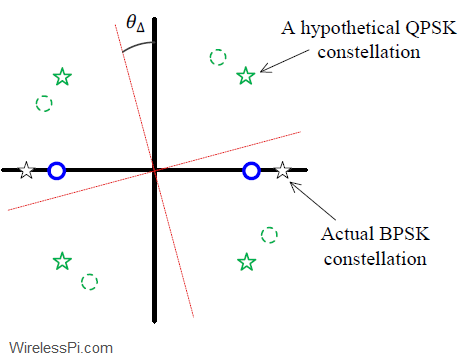

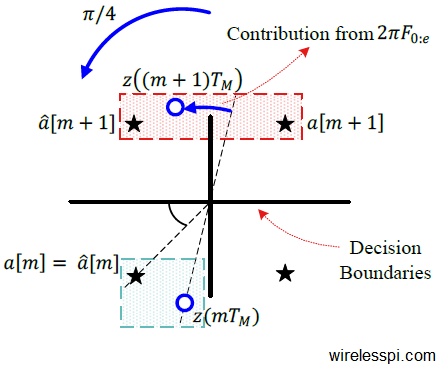

A carrier phase offset rotates the Rx constellation causing decision errors even in a perfectly noiseless environment. One of the techniques used to overcome this problem is to insert a known sequence at the start of the transmission known as a preamble. Then, the Rx can utilize these known symbols in the arriving signal to estimate the carrier phase and de-rotate the constellation. However, inserting a known sequence within the message decreases the spectral efficiency of the system. To avoid this cost, a phase estimator (as well as estimators for other distortions) can be derived in a non-data-aided fashion. One

Continue reading