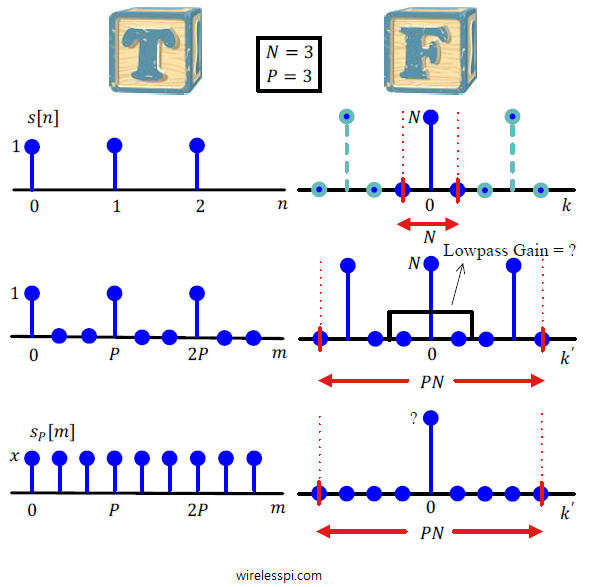

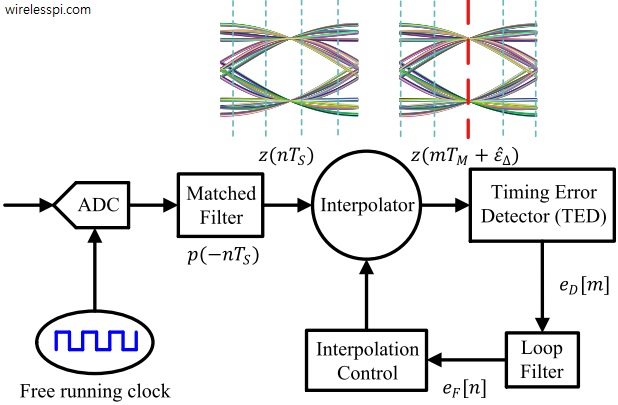

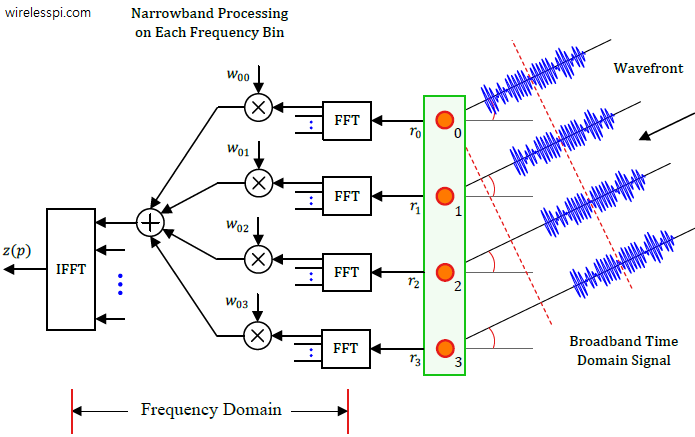

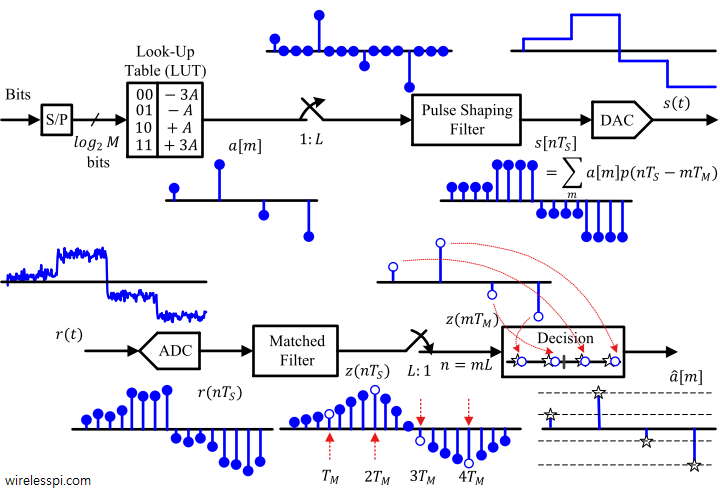

In the discussion on sampling, the process of sampling a continuous-time signal was discussed in detail and subsequently sampling theorem was derived. In many applications, resampling an already digitized signal is mandatory for an efficient system design. In wireless communications, sample rate conversion is utilized for upconversion and downconversion to a desired frequency, filtering stages in the digital frontend and sometimes for carrier and timing synchronization during signal acquisition. See the Cascade Integrator Comb (CIC) filters for how to accomplish this task with minimal resources. In discrete domain, sample rate can be reduced by discarding intermediate samples periodically called downsampling

Continue reading